- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Capas epitaxiales: la base de los dispositivos semiconductores avanzados

Figura 1: Ilustra la correlación entre las concentraciones de dopaje, el espesor de la capa y el voltaje de ruptura para dispositivos unipolares.

La preparación de capas epitaxiales de SiC abarca principalmente técnicas como el crecimiento por evaporación, la epitaxia en fase líquida (LPE), la epitaxia por haz molecular (MBE) y la deposición química de vapor (CVD), siendo la CVD el método predominante para la producción en masa en las fábricas.

Tabla 1: Proporciona una descripción comparativa de los principales métodos de preparación de la capa epitaxial.

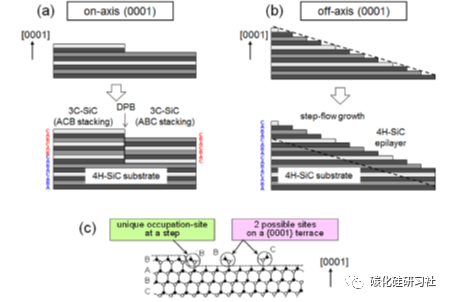

Un enfoque innovador implica el crecimiento en sustratos {0001} fuera del eje en un ángulo de inclinación específico, como se muestra en la Figura 2 (b). Este método aumenta significativamente la densidad de los pasos al tiempo que reduce el tamaño de los pasos, lo que facilita la nucleación principalmente en los sitios de agrupamiento de los pasos y, por lo tanto, permite que la capa epitaxial replique perfectamente la secuencia de apilamiento del sustrato, eliminando la coexistencia de politipos.

Figura 2: Demuestra el proceso físico de epitaxia controlada por pasos en 4H-SiC.

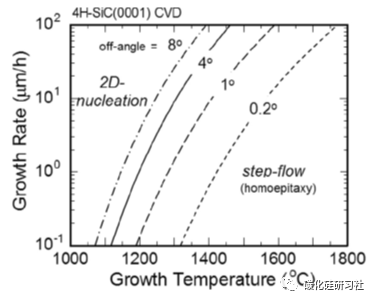

Figura 3: Muestra las condiciones críticas para el crecimiento de CVD en epitaxia controlada por pasos para 4H-SiC.

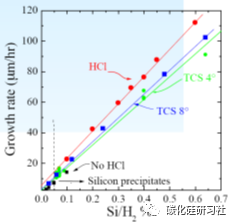

Figura 4: Compara las tasas de crecimiento con diferentes fuentes de silicio para la epitaxia 4H-SiC.

En el ámbito de las aplicaciones de baja y media tensión (por ejemplo, dispositivos de 1200 V), la tecnología de epitaxia de SiC ha alcanzado una etapa madura, ofreciendo una uniformidad relativamente superior en espesor, concentración de dopaje y distribución de defectos, cumpliendo adecuadamente con los requisitos para SBD de baja y media tensión. , dispositivos MOS, JBS y otros.

Sin embargo, el ámbito de la alta tensión todavía presenta desafíos importantes. Por ejemplo, los dispositivos clasificados a 10000 V requieren capas epitaxiales de aproximadamente 100 μm de espesor, pero estas capas exhiben un espesor y una uniformidad de dopaje considerablemente peores en comparación con sus contrapartes de bajo voltaje, sin mencionar el impacto perjudicial de los defectos triangulares en el rendimiento general del dispositivo. Las aplicaciones de alto voltaje, que tienden a favorecer los dispositivos bipolares, también imponen exigencias estrictas en la vida útil de los portadores minoritarios, lo que requiere la optimización del proceso para mejorar este parámetro.

Actualmente, el mercado está dominado por las obleas epitaxiales de SiC de 4 y 6 pulgadas, con un aumento gradual en la proporción de obleas epitaxiales de SiC de gran diámetro. El tamaño de las obleas epitaxiales de SiC está determinado fundamentalmente por las dimensiones de los sustratos de SiC. Con los sustratos de SiC de 6 pulgadas ahora disponibles comercialmente, la transición de la epitaxia de SiC de 4 a 6 pulgadas está en marcha de manera constante.

A medida que avanza la tecnología de fabricación de sustratos de SiC y se expanden las capacidades de producción, el costo de los sustratos de SiC disminuye progresivamente. Dado que los sustratos representan más del 50% del costo de las obleas epitaxiales, se espera que la disminución de los precios de los sustratos conduzca a menores costos para la epitaxia de SiC, prometiendo así un futuro mejor para la industria.**